集成电路设计流程 从概念到芯片的精密之旅

集成电路(IC),作为现代电子设备的核心,其设计是一个高度复杂、系统化和多阶段的工程过程。它不仅仅是电路图的绘制,更是一个融合了系统架构、电路设计、物理实现和验证测试的完整生命周期。一个典型的集成电路设计流程可以概括为以下几个关键阶段,它们环环相扣,共同确保最终芯片的功能、性能和可靠性。

第一阶段:系统规格定义与架构设计

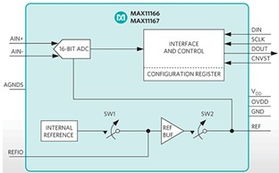

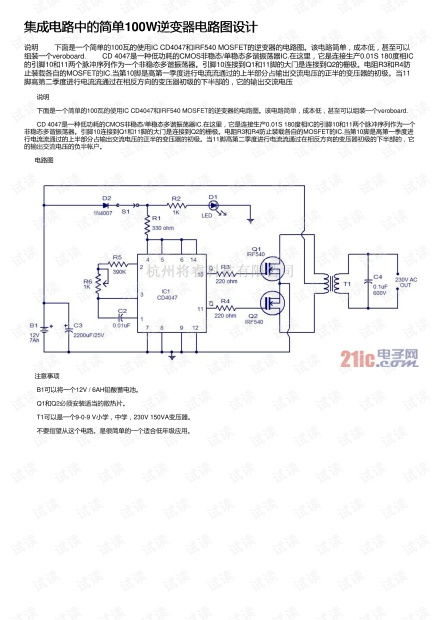

这是设计的起点,旨在回答“芯片要做什么?”和“要达到什么水平?”。设计团队需要与市场、应用工程师紧密合作,明确芯片的功能需求、性能指标(如速度、功耗)、成本目标、物理尺寸(封装形式)以及接口标准等。在此基础上,进行高层次架构设计,确定芯片的整体模块划分(如处理器核心、内存控制器、外设接口等),以及各模块之间的互连和数据流方案。此阶段通常使用高级建模语言(如SystemC、Matlab)进行算法验证和架构探索。

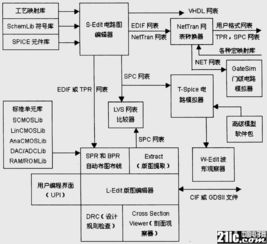

第二阶段:前端设计(逻辑设计)

前端设计将抽象的架构转化为具体的数字逻辑。此阶段主要包括两个核心步骤:

- 寄存器传输级设计:设计师使用硬件描述语言(HDL),如Verilog或VHDL,对各个功能模块进行“寄存器传输级”描述。RTL代码定义了数据如何在寄存器之间流动和进行逻辑处理,是电路功能的精确表述。

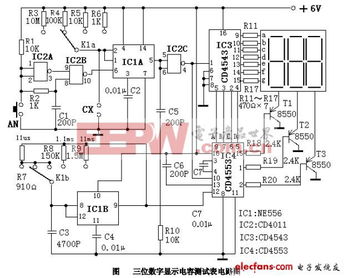

- 逻辑综合:将RTL代码输入综合工具,配合特定的工艺库(包含标准逻辑单元如与门、或门、触发器的时序、面积、功耗模型),工具会自动将其转换(综合)成由基本逻辑单元组成的门级网表。此阶段会进行初步的时序分析和优化,以确保逻辑功能正确并满足时钟频率要求。

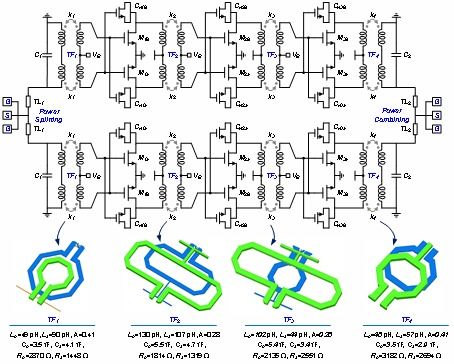

第三阶段:后端设计(物理设计)

后端设计负责将门级网表“放置”到实际的硅片平面上,并“连接”起来,生成可用于制造的版图数据。这是设计流程中最接近物理现实的步骤,主要包括:

- 布图规划与布局:规划芯片的整体版图,确定各个功能模块、电源网络、输入输出焊盘的位置。然后将综合后的数百万甚至数十亿个逻辑单元(标准单元)合理地摆放到芯片的版图上。

- 时钟树综合:构建一个低偏移、低功耗的全局时钟分布网络,确保时钟信号能够几乎同时到达所有时序单元(如触发器),这是保证芯片高速稳定运行的关键。

- 布线:根据逻辑连接关系(网表),在单元之间的缝隙中,使用多层金属连线将所有单元正确地连接起来。需要规避串扰、电迁移等问题。

- 物理验证:对生成的版图进行严格的验证,包括:

- 设计规则检查:确保版图符合芯片制造厂(Foundry)的工艺技术规则,保证可制造性。

- 版图与原理图比对:确认物理版图与原始逻辑网表在电气连接上完全一致。

- 寄生参数提取与时序分析:提取布线带来的电阻、电容等寄生效应,进行更精确的静态时序分析,确保在最坏情况下仍能满足时序要求。

- 电源完整性分析:检查电源网络的电压降和电迁移可靠性。

第四阶段:签核与流片

当所有验证都通过后,设计进入最终签核阶段。此时需要进行全面的、基于最终版图和提取的寄生参数的仿真与验证,包括时序、功耗、信号完整性等。一旦所有指标均达到规格要求,设计数据(通常是GDSII格式的版图文件)将被“冻结”,并发送给晶圆代工厂进行制造,这个过程被称为“流片”。流片成本高昂,周期长(数月),因此签核前的验证必须做到万无一失。

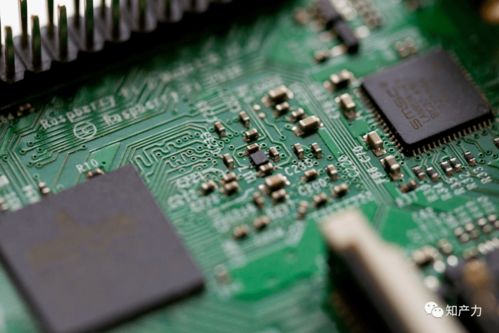

第五阶段:测试与封装

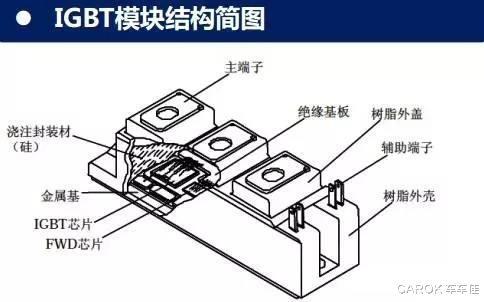

制造完成的硅晶圆经过切割,形成独立的芯片裸片。每一颗芯片都需要进行严格的测试,筛选出功能完好的芯片。然后,合格的裸片被封装到特定的外壳中,形成我们日常所见的芯片成品,并进行最终的成品测试。

贯穿全程:验证与电子设计自动化

需要强调的是,验证活动贯穿于上述所有阶段,从系统级仿真、RTL功能仿真、形式验证到物理验证,其工作量往往占到整个设计项目的70%以上,是保证设计成功的关键。整个流程极度依赖电子设计自动化工具链,包括仿真器、综合工具、布局布线工具、验证平台等,它们极大地提升了设计的效率和可靠性。

总而言之,集成电路设计流程是一个从抽象到具体、从行为到结构、从逻辑到物理的逐级细化与迭代优化的过程。它凝聚了系统架构师、数字设计工程师、物理设计工程师、验证工程师等多领域专家的智慧与协作,是工程学与精密制造的典范,最终将创新的想法转化为实实在在驱动数字世界的硅基芯片。

如若转载,请注明出处:http://www.yunguochuxing.com/product/56.html

更新时间:2026-04-14 14:01:05